The integration of electronic chips in commercial devices has significantly evolved over the past decades, with engineers devising various integration strategies and solutions. Initially, computers contained a central processor or central processing unit (CPU), connected to memory units and other components via traditional communication pathways, known as front-side-bus (FSB) interfaces.

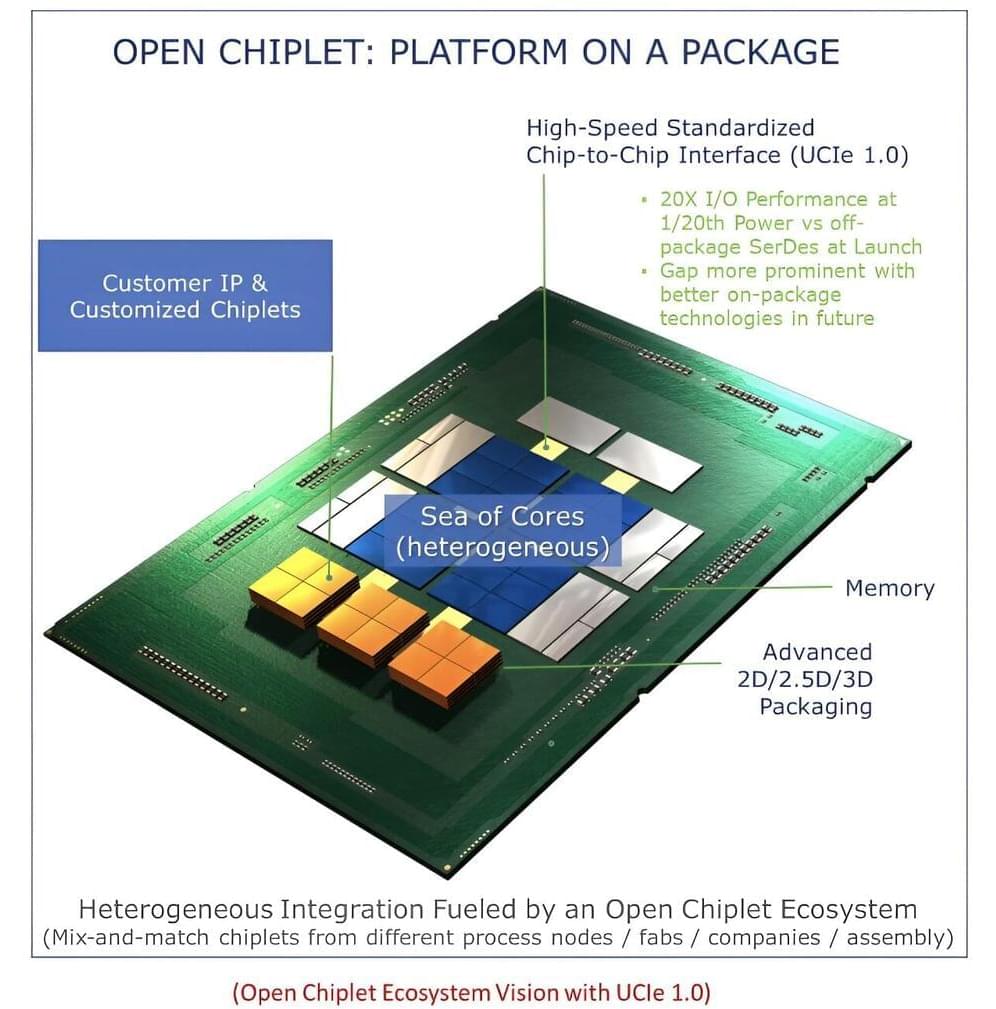

Technological advances, however, have enabled the development of new integrated circuit (IC) architectures relying on multiple chiplets and more sophisticated electronic components. Intel Corporation played a crucial role in these developments, by introducing new architectures and specifications for the design of systems with multiple packaged chiplets.

Researchers at Intel Corporation Santa Clara recently outlined a new vision for further boosting the performance of systems developed following universal chiplet interconnect express (UCIe), a specification to standardize the connections between multi-function chiplets in modern System-in-Package (SiP). Their proposed approach, presented in a paper in Nature Electronics, entails reducing the frequency in these circuits to boost their power efficiency and performance.