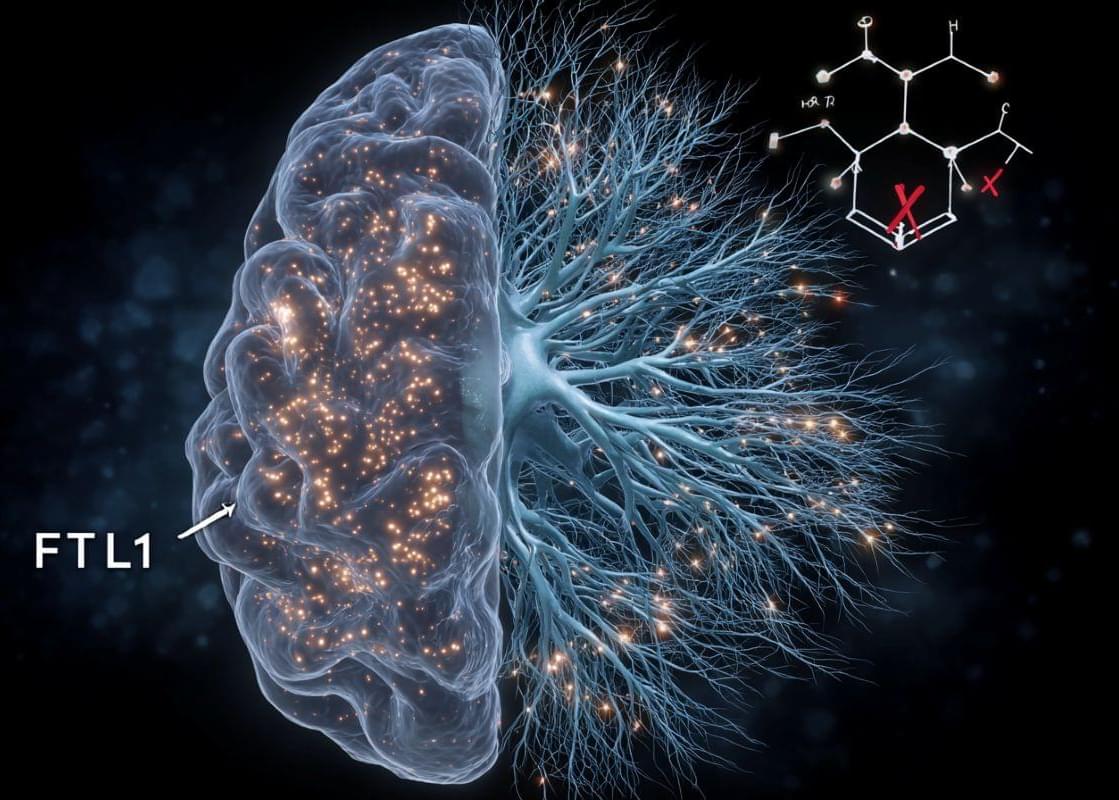

Could pig plasma fractions really rejuvenate aging rats? Join me as I interview Nicolás and Nina from the Rejuvenation Science Institute (Brazil), who are working to reproduce the headline-creating “pig plasma rejuvenation” results. We explore the origins, science, controversies, challenges, and hopes surrounding this research—plus their plans for the next breakthrough longevity experiment and open science collaboration.

https://www.rejuvenescimento.org/english.

https://www.rejuvenescimento.org/news… https://journals.tmkarpinski.com/inde… Timestamps 00:00 – Introduction: The Pig Plasma Rat Rejuvenation Debate 02:00 – Origins: Why try to reproduce these results? 08:30 – What is being injected? Fraction preparation explained 15:40 – Acute toxicity and safety results: did the rats survive? 26:00 – The next experiment: timelines, scale-up, and open science goals Find me on Twitter — / eleanorsheekey Support the channel through PayPal — https://paypal.me/sheekeyscience?coun… through Patreon —

/ thesheekeyscienceshow Please note that The Sheekey Science Show is distinct from Eleanor Sheekey’s teaching and research roles. The information provided in this show is not medical advice, nor should it be taken or applied as a replacement for medical advice. The Sheekey Science Show and guests assume no liability for the application of the information discussed. Icons in intro; “https://www.freepik.com/free-photos-v…Background“Background vector created by freepik — www.freepik.com.

https://journals.tmkarpinski.com/inde…

Timestamps.

00:00 – Introduction: The Pig Plasma Rat Rejuvenation Debate.

02:00 – Origins: Why try to reproduce these results?

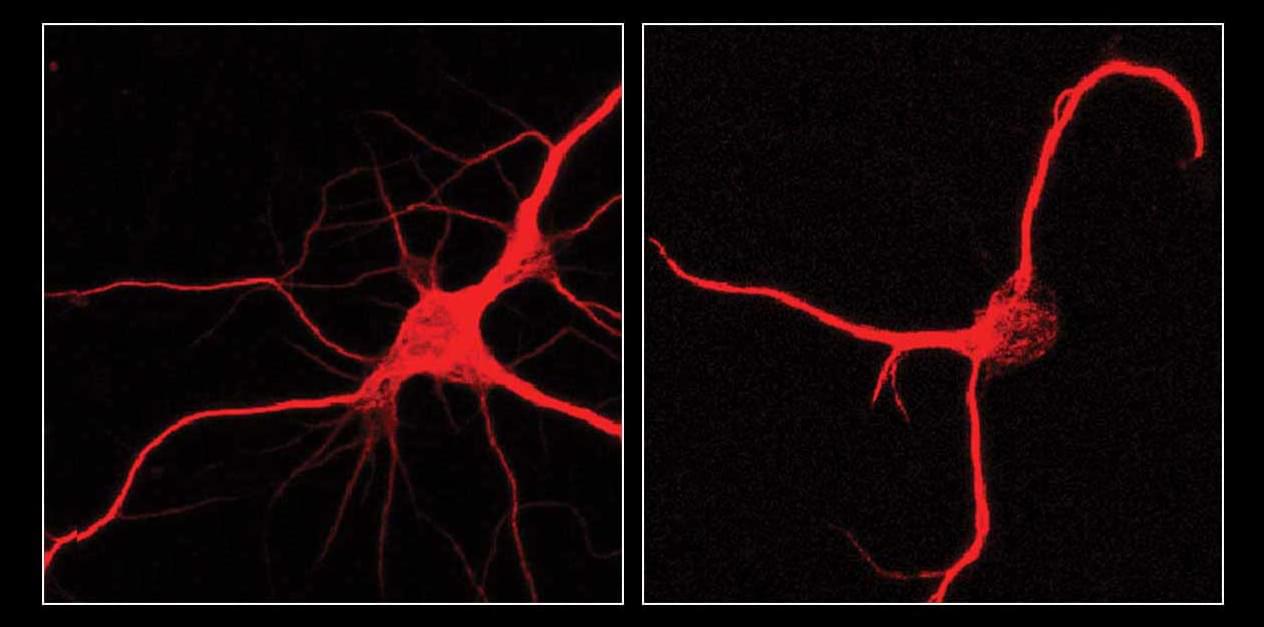

08:30 – What is being injected? Fraction preparation explained.

15:40 – Acute toxicity and safety results: did the rats survive?

26:00 – The next experiment: timelines, scale-up, and open science goals.

Find me on Twitter — / eleanorsheekey.

Support the channel.

through PayPal — https://paypal.me/sheekeyscience?coun…

through Patreon — / thesheekeyscienceshow.

Please note that The Sheekey Science Show is distinct from Eleanor Sheekey’s teaching and research roles. The information provided in this show is not medical advice, nor should it be taken or applied as a replacement for medical advice. The Sheekey Science Show and guests assume no liability for the application of the information discussed.

Icons in intro; \.